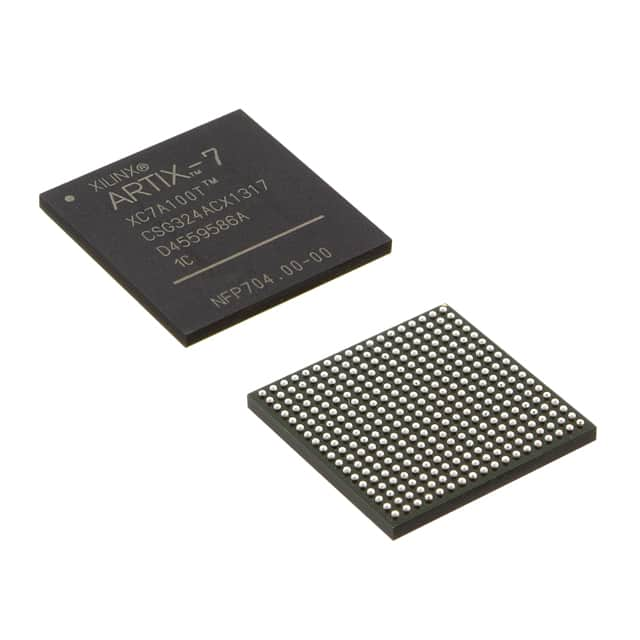

Oriģinālā IC mikroshēma Programmējama XCVU440-2FLGA2892I IC FPGA 1456 I/O 2892FCBGA

Produkta atribūti

| VEIDS | APRAKSTS |

| Kategorija | Integrētās shēmas (IC) |

| Mfr | AMD Xilinx |

| sērija | Virtex® UltraScale™ |

|

| Kaste |

| Standartsd Iepakojums | 1 |

| Produkta statuss | Aktīvs |

| LAB/CLB skaits | 316620 |

| Loģisko elementu/šūnu skaits | 5540850 |

| Kopējie RAM biti | 90726400 |

| I/O skaits | 1456. gads |

| Spriegums – barošana | 0,922V ~ 0,979V |

| Montāžas veids | Virsmas stiprinājums |

| Darbības temperatūra | -40°C ~ 100°C (TJ) |

| Iepakojums / futrālis | 2892-BBGA, FCBGA |

| Piegādātāja ierīču pakete | 2892-FCBGA (55 × 55) |

| Pamatprodukta numurs | XCVU440 |

FPGA izmantošana kā trafika procesori tīkla drošībai

Satiksme uz un no drošības ierīcēm (ugunsmūriem) tiek šifrēta vairākos līmeņos, un L2 šifrēšana/atšifrēšana (MACSec) tiek apstrādāta saites slāņa (L2) tīkla mezglos (slēdži un maršrutētāji).Apstrāde ārpus L2 (MAC slānis) parasti ietver dziļāku parsēšanu, L3 tuneļa atšifrēšanu (IPSec) un šifrētu SSL trafiku ar TCP/UDP trafiku.Pakešu apstrāde ietver ienākošo pakešu parsēšanu un klasificēšanu, kā arī lielu trafika apjomu (1–20 M) apstrādi ar augstu caurlaidspēju (25–400 Gb/s).

Tā kā ir nepieciešams liels skaits skaitļošanas resursu (kodolu), NPU var izmantot salīdzinoši lielāka ātruma pakešu apstrādei, taču zema latentuma, augstas veiktspējas mērogojamā trafika apstrāde nav iespējama, jo trafika apstrāde tiek veikta, izmantojot MIPS/RISC kodolus un plānojot šādus kodolus. pamatojoties uz to pieejamību, ir grūti.Uz FPGA balstītu drošības ierīču izmantošana var efektīvi novērst šos CPU un NPU balstītu arhitektūru ierobežojumus.

Lietojumprogrammu līmeņa drošības apstrāde FPGA

FPGA ir ideāli piemēroti integrētai drošības apstrādei nākamās paaudzes ugunsmūros, jo tie veiksmīgi apmierina vajadzību pēc augstākas veiktspējas, elastības un zemas latentuma darbības.Turklāt FPGA var ieviest arī lietojumprogrammu līmeņa drošības funkcijas, kas var vēl vairāk ietaupīt skaitļošanas resursus un uzlabot veiktspēju.

Kopējie lietojumprogrammu drošības apstrādes piemēri FPGA ietver

- TTCP izkraušanas dzinējs

- Regulāro izteiksmju saskaņošana

- Asimetriskās šifrēšanas (PKI) apstrāde

- TLS apstrāde

Nākamās paaudzes drošības tehnoloģijas, izmantojot FPGA

Daudzi esošie asimetriskie algoritmi ir neaizsargāti pret kvantu datoru kompromisiem.Kvantu skaitļošanas metodes visvairāk ietekmē asimetriskos drošības algoritmus, piemēram, RSA-2K, RSA-4K, ECC-256, DH un ECCDH.Tiek pētītas jaunas asimetrisko algoritmu ieviešanas un NIST standartizācijas.

Pašreizējie priekšlikumi pēckvantu šifrēšanai ietver Ring-on-Error Learning (R-LWE) metodi

- Publiskās atslēgas kriptogrāfija (PKC)

- Ciparparaksti

- Atslēgu izveide

Piedāvātā publiskās atslēgas kriptogrāfijas realizācija ietver noteiktas labi zināmas matemātiskas darbības (TRNG, Gausa trokšņu izlases ņēmējs, polinoma saskaitīšana, binārā polinoma kvantora dalīšana, reizināšana utt.).FPGA IP daudziem no šiem algoritmiem ir pieejams vai to var efektīvi ieviest, izmantojot FPGA blokus, piemēram, DSP un AI dzinējus (AIE) esošajās un nākamās paaudzes Xilinx ierīcēs.

Šajā baltajā grāmatā ir aprakstīta L2-L7 drošības ieviešana, izmantojot programmējamu arhitektūru, ko var izvietot drošības paātrināšanai malas/piekļuves tīklos un nākamās paaudzes ugunsmūrēs (NGFW) uzņēmumu tīklos.